中国计算机学会推荐B类国际会议International Conference on Parallel Processing(ICPP 2020)近期录用了华中科技大学武汉光电国家研究中心冯丹教授课题组博士生魏学亮为第一作者的研究成果“CCHL: Compression-Consolidation Hardware Logging for Efficient Failure-Atomic Persistent Memory Updates”。此次会议收到的总投稿数为269篇,最终录用78篇,录用率为29%。

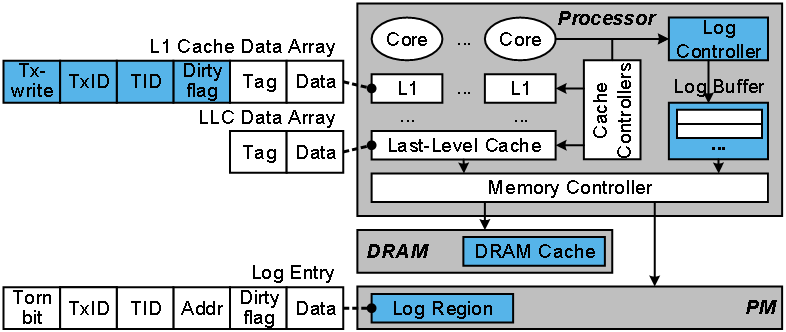

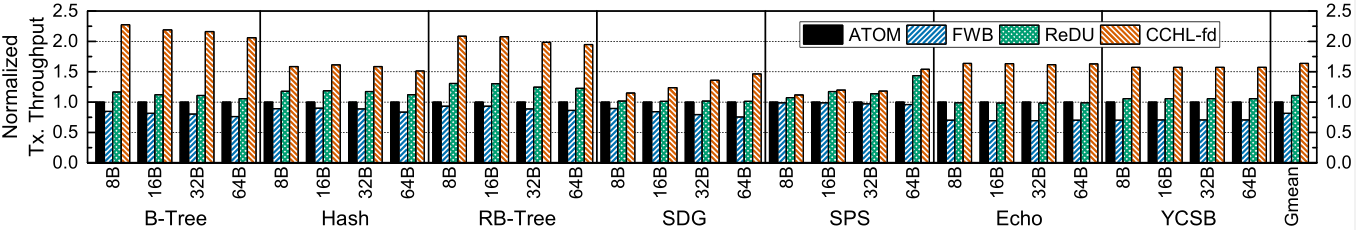

研究如何将新型字节可寻址的非易失存储器(Non-Volatile Memory,NVM)放置在内存总线上作为持久性内存(Persistent Memory,PM)使用是当前的研究热点,但基于PM的内存系统需要提供故障原子更新的支持。针对现有硬件日志机制在事务执行的关键路径上执行许多日志写操作,从而导致不可忽视的性能开销的问题,武汉光电国家研究中心冯丹教授课题组提出了一种避免非必要日志写操作、避免在关键路径上持久化日志的硬件日志方案(称为CCHL),显著减少了PM写操作数量并提升了系统整体性能。图1所示为CCHL的整体系统结构示意图。为了避免非必要日志写操作,CCHL采用了两种日志优化策略:事务内日志压缩、事务间日志合并。事务内日志压缩策略只为事务内会修改数据的值的写操作创建日志项,并在日志项中只保存数据值被修改的部分。事务间日志合并策略能够合并地址相同的写操作对应的日志项,即使这些日志项来自不同事务。为了避免在关键路径上持久化日志,CCHL利用推迟耐久性,在事务提交时不等待日志写操作的持久化,并使用DRAM的部分空间缓存日志写操作。当推迟耐久性的事务数量超过预定阈值后,CCHL在后台将缓存的日志写操作写回PM。如图2所示,基于Gem5+NVMain全系统仿真平台的测试结果表明,相比于最新的Redo硬件日志方案,CCHL能够达到平均47.8%的性能提升。

图1 CCHL的整体系统结构

图2 Micro-Benchmarks和Macro-Benchmarks负载下的性能对比

本研究工作得到了国家自然科学基金、中央高校基本科研专项资金、国家科技重大专项等项目资助。

分享文章

分享文章  最新发布

最新发布  友情链接

友情链接