随着闪存工艺尺寸的缩小以及单元内多比特存储技术的发展,闪存芯片的容量逐渐增加,但闪存的可靠性问题变得更加严重。固态硬盘(Solid State Driver,SSD)内部现有的可靠性方案(如ECC、RAID)不能很好的应对闪存的多级可靠性问题;另外,固定的可靠性方案未考虑块间磨损不平衡:在SSD前期提供了过多的冗余,从而增加了闪存的写放大,并且在SSD后期也不能容忍条带内出现多个错误的情况。

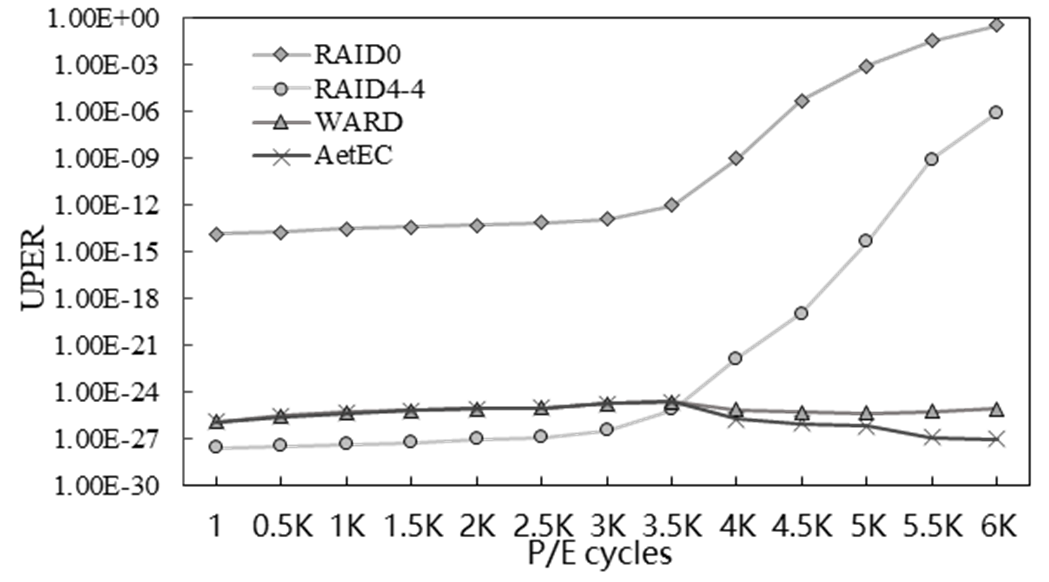

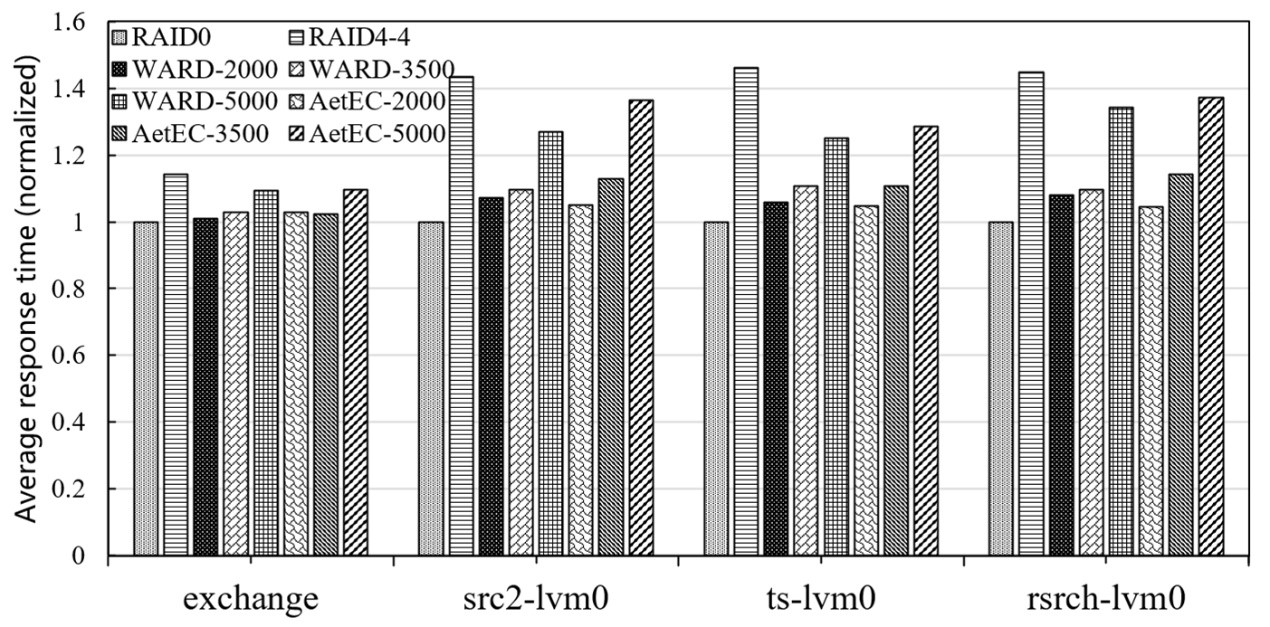

信息存储与光显示功能实验室博士生詹天奇、硕士生王先鹏,在冯丹教授、童薇副教授的指导下设计实现了一种自适应容错的SSD纠删码方案(Adaptive error-tolerant Erasure Coding Scheme Within SSDs,AetEC)。在SSD寿命前期,通过实时监测闪存块的磨损情况,并根据超级块中的高磨损块数应用相应纠错能力的RS(Reed Solomon)纠删码;在SSD寿命后期,将RS码的容错能力调至最大,以容忍芯片级故障。基于物理地址的条带组织方案有效地减少了校验数据的更新开销;基于双链表分区管理的写缓存方案在提高SSD性能的同时,保证了用户数据和校验数据的一致性;针对不同的错误类型,设计了不同的数据恢复方法和数据重建布局方法。另外,考虑到软件实现的RS码会对SSD的高性能造成很大的影响,设计了一种基于FPGA的多速率RS码的编/解码器方案。对多种RS码的解码矩阵进行预处理以省去解码矩阵的求解过程,并采用基址加变址寻址的思想优化解码矩阵索引的计算过程,使得解码和编码具有几乎一样的吞吐率。

该研究于2020年8月被IEEE International Conference on Computer Design (IEEE ICCD)以长文录用,题为“AetEC: Adaptive error-tolerant Erasure Coding Scheme Within SSDs”,获最佳论文提名。ICCD是计算机体系结构领域重要的国际学术会议之一。

图1 AetEC整体架构

图2 AetEC与对比方案的可靠性

图3 AetEC的处理时间对比图

研究工作得到了国家自然科学基金和中央高校基本科研专项资金等项目的资助。

分享文章

分享文章  最新发布

最新发布  友情链接

友情链接